比科奇5G小基站SoC集成UltraSoC系統(tǒng)監(jiān)測(cè)IP,賦能軟件開(kāi)發(fā)效率提升

近日,半導(dǎo)體設(shè)計(jì)企業(yè)比科奇(Picochip)宣布在其新一代5G New Radio小基站系統(tǒng)級(jí)芯片(SoC)中,選用UltraSoC先進(jìn)的系統(tǒng)駐留分析與監(jiān)測(cè)知識(shí)產(chǎn)權(quán)(IP)模塊。這一技術(shù)決策旨在顯著提升小基站軟件的開(kāi)發(fā)調(diào)試效率與系統(tǒng)可靠性。

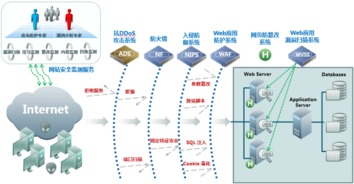

隨著5G網(wǎng)絡(luò)向高密度、低延遲場(chǎng)景擴(kuò)展,小基站作為宏基站的補(bǔ)充,其芯片的實(shí)時(shí)性能與穩(wěn)定性變得尤為關(guān)鍵。比科奇此次集成的UltraSoC IP具備深度嵌入式分析能力,可對(duì)SoC內(nèi)部處理器的代碼執(zhí)行、數(shù)據(jù)流和系統(tǒng)事件進(jìn)行非侵入式監(jiān)測(cè)。通過(guò)實(shí)時(shí)追蹤軟件在核心中的駐留行為,開(kāi)發(fā)團(tuán)隊(duì)能夠快速定位性能瓶頸、優(yōu)化代碼效率,并提前識(shí)別潛在的系統(tǒng)異常。

在5G小基站的復(fù)雜多任務(wù)環(huán)境中,傳統(tǒng)調(diào)試工具往往難以捕捉瞬時(shí)性問(wèn)題。UltraSoC的解決方案通過(guò)在硬件層面嵌入監(jiān)測(cè)邏輯,實(shí)現(xiàn)了對(duì)運(yùn)行時(shí)行為的連續(xù)可視化,大幅縮短了故障排查周期。比科奇工程師可借助該IP生成詳細(xì)的分析報(bào)告,精細(xì)調(diào)整基站軟件的調(diào)度算法與資源分配策略,從而滿(mǎn)足5G NR嚴(yán)格的時(shí)序與吞吐量要求。

這一合作不僅強(qiáng)化了比科奇小基站SoC的差異化競(jìng)爭(zhēng)力,也為5G開(kāi)放式無(wú)線接入網(wǎng)(O-RAN)架構(gòu)的部署提供了更可靠的底層支撐。通過(guò)將系統(tǒng)級(jí)監(jiān)測(cè)能力融入芯片設(shè)計(jì),比科奇與UltraSoC共同推動(dòng)了5G小基站開(kāi)發(fā)模式從“黑盒調(diào)試”向“透明化分析”的演進(jìn),為全球5G網(wǎng)絡(luò)的高效建設(shè)注入創(chuàng)新動(dòng)力。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.hjzd131419.com.cn/product/1.html

更新時(shí)間:2026-04-08 21:30:12